- IC�ͺ�

��ҵ����

- ���֤����

- ��Ա���ͣ���ͨ��Ա

- ��ַ���ɿ�13��˰Ʊ��ֻ��ԭװ�ֻ������� �������и�������ǿ��·Ⱥ�ǹ㳡101��5¥508

- ���棺0755-82767516

- E-mail��szhmw168@163.com

��Ʒ����

���ɵ�·(IC)(8)��ԴIC(2)�뵼��洢��(2)������(2)������(2)�Ŵ���(2)�����/����/����(1)LED(1)

- ��ѹ������(1)

- Ф�ػ�������(1)

- ����������(1)

- ���Դ�����(1)

- LED����(1)

����ʽ���ָ������ļ���Ʒ���

����ʱ�䣺 2019/6/6 9:42:55 | 343 ���Ķ�

Ŀǰ���й������豸ʹ�ú���Ƶİ�ȫ�涨������ʹ����������������Ϊ�������ݲɼ��ʹ���ϵͳ�еı��衣�������ϵͳ��ѹ��·�ڵ糡������DZ�ڵĴ������ʹ����������ѹ��һ�ַ���������ʹ�����ָ�������

���ĵ�Ŀ�����ڸ��ߴ����μ���ϵͳ��ƣ����³���������ʽ���ָ������Ļ������ܣ���ϸ����������ź�ͨ·�а�װ�������⣬������ɹ���Ƶ�·���ṩ��һЩ�м�ֵ�IJο������

����ʽ���ָ������Ļ�������

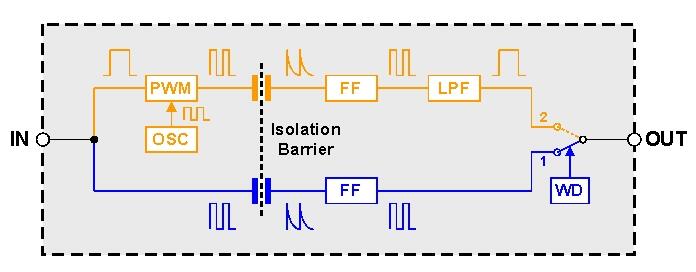

ͼ1��ʾ��һ������ʽ���ָ������ļṹͼ���ø�������һ�������ź�·����һ�������ź�·����ɡ�����·������ɫ���֣�����100kbps��150Mbps���źţ�������·������ɫ���֣�����100kbps�����ź���dc��

��ɫ������ʾ·���д����ĸ����źű�����ʽ�������ݷ�Ϊ�������˲������Ⱥ�����Ĵ�������FF������Щ˲̬����Ⱥת���ɲ��κ���λ���������ź�һ�µ����塣�ڲ����Ź���WD���������źű�Ե�������ԡ��ڵ�Ƶ�����ź�����£������źű�Ե��ij���ʱ�䳬���˿��Ź����ڡ���������ʹ���Ź����������λ�ôӸ���·����λ��1���ı�Ϊ����·����λ��2����

����·���ȸ���·�������������Ԫ������Ϊ��Ƶ�����ź�Ҫ��������ݽ�ֹ���ô���ݣ����������źű����ڶ��ڲ�������OSC�����ز�Ƶ�ʽ����������ƣ�PWM�����������һ���dz��ߵ�Ƶ�ʣ��ܹ�ͨ���õ������ݡ���������õ��˵��ƣ���˱�����ʵ�����ݴ������������ǰʹ�õ�ͨ�˲�����LPF��ȥ�����еĸ�Ƶ�ز���

���ź����еİ�װλ��

���ָ�������Ϊ��ͨ����˫ͨ������ͨ������ͨ������������ʵ�ֵ����˫�����У����ǵĹ����������£�

- �������κ��ض��ӿڱ���

- ʹ��3V/5V�����ؼ���

- רΪ��������֡����ˣ�SE�������߶����

��Ȼһ���ƺ�������ϵ����ƣ�Ȼ��ͼ2ȴ��ʾ����ζԶ��ֽӿڽ��и��룬���а�����ѹ SPI����ѹRS232�����USB�Ͳ��CAN/RS485��

���нӿڶ���һ����ͬ�㣬�Ǿ������ָ��������밲װ�ڸ���ӿڵĵ���3V/5V���֡�

�������ָ�����������1��2ns������ʱ�䣬��������ڳ��ź���������������׳����źŷ��䣬�������迹������������Դ�迹��ƥ�䡣��ˣ����ǽ���������Ӧ���ݽ���װ�ú�����Դ�����磺�������������������������շ����ȣ�������װһ��������������������������������ô�ͱ���ʹ���ܿص��迹�����ߡ�

PCB ���ָ��

�����ֵ�·����ԣ�Ҫʹ�ñ�FR-4����������ΪPCB���ϣ��������������Щ���۲��ϣ��䲻������UL94-V0Ҫ���һ�ӵ�и��ٵĸ�Ƶ�����ġ����͵���ʪ�ԡ������ǿ/Ӳ���Լ����ߵ���ȼ���ԡ�

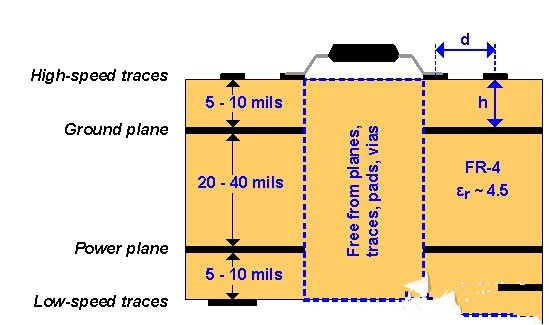

Ҫʵ�ֵ͵�Ÿ��ţ�EMI����PCB��ƣ������Ƽ�һ�����IJ�����ʵ������μ�ͼ3��������ϵ��·ֱ�Ϊ�������źŲ㡢�ӵز㡢��Դ���Լ���Ƶ�źŲ㡣

�ڶ��㲼�ø�������Ϊ������������Ӧ���������ṩ��һĿ��Ȼ�����ӡ���������Ҫ�̣�������ʹ�ù��ף��Դ˱�֤�������ߵ�С�

�����Ÿ����źŲ����һ��ƽ�������߲㣬��ȷ���ӵز���ź�����֮�����ǿ��ĵ�����ϡ������㽨�������������ܿ��迹��ͬʱҲ����ؼ�����EMI���գ�ƽ�������߲�Ϊ�����ṩ��һ���dz��õĵ͵��·����

����Դ�����ڽӵز����档�������ο��㹹����һ����ԼΪ100pF/in2�ĸ��Ӹ�Ƶ��·��������

�ڵײ㲼�ߵ��ٿ����źš���Щ�ź���·ӵ���㹻�����������ܹ���������жϣ��Ӷ�ʵ���˸��������ԡ�

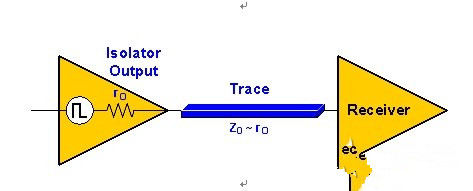

�ܿ��迹�������������迹Z0ʼ���ܿ����伸�����Ե����ߡ����߳��ȴ���15mm��tr=1ns���� 30mm��tr=2ns��ʱ�������迹����Ҫ�����������迹Z0~rOƥ�䣨��ͼ4��ʾ����ʹ�źŷ��仯���ⱻ��ΪԴ�迹ƥ�䡣

�������Ķ�̬����迹r0������ͨ�������������ֲ����г��Ľ��Ƶ�ѹ-��������������Բ��ֵõ���һ����˵��������迹��ԼΪ70������ˣ���һ������2��˾��ͭ�ߺ͵����Ϊ4.5��FR-4���ԣ��ӵز���8mm����10mm������������״����������70�������迹��

����ָ��

������ѭ���м�����Ҫ�IJ���ԭ���Ա����ź������Ժ͵�EMI��

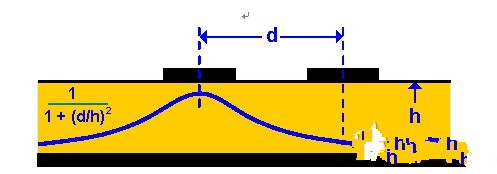

Ϊ�˽����Ž���10%���£��豣���ź������Ǹ����źŲ㵽�ӵز�����������d=3h�����ź������µĻ����ܶ���ѭ1/��1+��d/h��2�ݺ������������d��3h���ϵ��ܶȻ�dz��ͣ��Ӷ������ڽ������г��ֽϴ�Ĵ��ţ���μ�ͼ5����

ʹ��45����������������б��ʽ����������90���������ɱ�����Ч�������迹�������źŷ��䡣

Ϊ��ʵ�������������µĹ���������������������������ͨ��һ����������1k����10k�������ӵ����ʵIJο��㡣���ߵ�ƽ��Ч����λ�����������ӵ���Դ�㣬ͬʱ���͵�ƽ��Ч�����������ӵز㡣

������������ź�·�����ʱ��Ҫ�������������ź����߸ı䡣

�ڸ���������Χ��·֮��ʹ�ý϶̵����߳��ȿɱ����������롣���ָ�����ͨ������и���ʽDC/DCת�����������ṩ�˿�Խ�����ĵ�Դ�����ڸ������ĵ��˴����źŶ���������������У�����ڽ�DC/DCת�����Ŀ����������Ժ����ױ����ź��������롣

�����������ݣ�����10��F�����ڿ�����Դ����ѹ���ԣ������ڵ�Դ����PCB�ĵط���

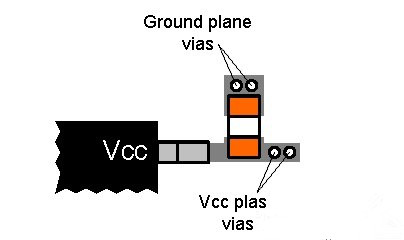

ͨ�������ݵĵ�Դ��ֱ�������������ĵ�Դ�ˣ�Ȼ��������Vcc�㣬�������ϰ�װС������0.1��F��0.01��F��·���ݡ��������������ݽӵض��������ӵز㣨��μ�ͼ6����

�������������������·���ݺ������������������磺˲̬��ѹ�����������������������Ӷ����ӵ����ӵĹ���С�

�ܽ�

���ܹ���PCB��Ƶ������кܶ࣬��������Ҫ�ṩһЩ�漰���ָ�������·����ƵĽ��顣��ѭ��Щ���齫�������ڶ̵�ʱ�������һ������EMC��Ҫ��ĵ�·����ơ�

���ĵ�Ŀ�����ڸ��ߴ����μ���ϵͳ��ƣ����³���������ʽ���ָ������Ļ������ܣ���ϸ����������ź�ͨ·�а�װ�������⣬������ɹ���Ƶ�·���ṩ��һЩ�м�ֵ�IJο������

����ʽ���ָ������Ļ�������

ͼ1��ʾ��һ������ʽ���ָ������ļṹͼ���ø�������һ�������ź�·����һ�������ź�·����ɡ�����·������ɫ���֣�����100kbps��150Mbps���źţ�������·������ɫ���֣�����100kbps�����ź���dc��

��ɫ������ʾ·���д����ĸ����źű�����ʽ�������ݷ�Ϊ�������˲������Ⱥ�����Ĵ�������FF������Щ˲̬����Ⱥת���ɲ��κ���λ���������ź�һ�µ����塣�ڲ����Ź���WD���������źű�Ե�������ԡ��ڵ�Ƶ�����ź�����£������źű�Ե��ij���ʱ�䳬���˿��Ź����ڡ���������ʹ���Ź����������λ�ôӸ���·����λ��1���ı�Ϊ����·����λ��2����

����·���ȸ���·�������������Ԫ������Ϊ��Ƶ�����ź�Ҫ��������ݽ�ֹ���ô���ݣ����������źű����ڶ��ڲ�������OSC�����ز�Ƶ�ʽ����������ƣ�PWM�����������һ���dz��ߵ�Ƶ�ʣ��ܹ�ͨ���õ������ݡ���������õ��˵��ƣ���˱�����ʵ�����ݴ������������ǰʹ�õ�ͨ�˲�����LPF��ȥ�����еĸ�Ƶ�ز���

���ź����еİ�װλ��

���ָ�������Ϊ��ͨ����˫ͨ������ͨ������ͨ������������ʵ�ֵ����˫�����У����ǵĹ����������£�

- �������κ��ض��ӿڱ���

- ʹ��3V/5V�����ؼ���

- רΪ��������֡����ˣ�SE�������߶����

��Ȼһ���ƺ�������ϵ����ƣ�Ȼ��ͼ2ȴ��ʾ����ζԶ��ֽӿڽ��и��룬���а�����ѹ SPI����ѹRS232�����USB�Ͳ��CAN/RS485��

���нӿڶ���һ����ͬ�㣬�Ǿ������ָ��������밲װ�ڸ���ӿڵĵ���3V/5V���֡�

�������ָ�����������1��2ns������ʱ�䣬��������ڳ��ź���������������׳����źŷ��䣬�������迹������������Դ�迹��ƥ�䡣��ˣ����ǽ���������Ӧ���ݽ���װ�ú�����Դ�����磺�������������������������շ����ȣ�������װһ��������������������������������ô�ͱ���ʹ���ܿص��迹�����ߡ�

PCB ���ָ��

�����ֵ�·����ԣ�Ҫʹ�ñ�FR-4����������ΪPCB���ϣ��������������Щ���۲��ϣ��䲻������UL94-V0Ҫ���һ�ӵ�и��ٵĸ�Ƶ�����ġ����͵���ʪ�ԡ������ǿ/Ӳ���Լ����ߵ���ȼ���ԡ�

Ҫʵ�ֵ͵�Ÿ��ţ�EMI����PCB��ƣ������Ƽ�һ�����IJ�����ʵ������μ�ͼ3��������ϵ��·ֱ�Ϊ�������źŲ㡢�ӵز㡢��Դ���Լ���Ƶ�źŲ㡣

�ڶ��㲼�ø�������Ϊ������������Ӧ���������ṩ��һĿ��Ȼ�����ӡ���������Ҫ�̣�������ʹ�ù��ף��Դ˱�֤�������ߵ�С�

�����Ÿ����źŲ����һ��ƽ�������߲㣬��ȷ���ӵز���ź�����֮�����ǿ��ĵ�����ϡ������㽨�������������ܿ��迹��ͬʱҲ����ؼ�����EMI���գ�ƽ�������߲�Ϊ�����ṩ��һ���dz��õĵ͵��·����

����Դ�����ڽӵز����档�������ο��㹹����һ����ԼΪ100pF/in2�ĸ��Ӹ�Ƶ��·��������

�ڵײ㲼�ߵ��ٿ����źš���Щ�ź���·ӵ���㹻�����������ܹ���������жϣ��Ӷ�ʵ���˸��������ԡ�

�ܿ��迹�������������迹Z0ʼ���ܿ����伸�����Ե����ߡ����߳��ȴ���15mm��tr=1ns���� 30mm��tr=2ns��ʱ�������迹����Ҫ�����������迹Z0~rOƥ�䣨��ͼ4��ʾ����ʹ�źŷ��仯���ⱻ��ΪԴ�迹ƥ�䡣

�������Ķ�̬����迹r0������ͨ�������������ֲ����г��Ľ��Ƶ�ѹ-��������������Բ��ֵõ���һ����˵��������迹��ԼΪ70������ˣ���һ������2��˾��ͭ�ߺ͵����Ϊ4.5��FR-4���ԣ��ӵز���8mm����10mm������������״����������70�������迹��

����ָ��

������ѭ���м�����Ҫ�IJ���ԭ���Ա����ź������Ժ͵�EMI��

Ϊ�˽����Ž���10%���£��豣���ź������Ǹ����źŲ㵽�ӵز�����������d=3h�����ź������µĻ����ܶ���ѭ1/��1+��d/h��2�ݺ������������d��3h���ϵ��ܶȻ�dz��ͣ��Ӷ������ڽ������г��ֽϴ�Ĵ��ţ���μ�ͼ5����

ʹ��45����������������б��ʽ����������90���������ɱ�����Ч�������迹�������źŷ��䡣

Ϊ��ʵ�������������µĹ���������������������������ͨ��һ����������1k����10k�������ӵ����ʵIJο��㡣���ߵ�ƽ��Ч����λ�����������ӵ���Դ�㣬ͬʱ���͵�ƽ��Ч�����������ӵز㡣

������������ź�·�����ʱ��Ҫ�������������ź����߸ı䡣

�ڸ���������Χ��·֮��ʹ�ý϶̵����߳��ȿɱ����������롣���ָ�����ͨ������и���ʽDC/DCת�����������ṩ�˿�Խ�����ĵ�Դ�����ڸ������ĵ��˴����źŶ���������������У�����ڽ�DC/DCת�����Ŀ����������Ժ����ױ����ź��������롣

�����������ݣ�����10��F�����ڿ�����Դ����ѹ���ԣ������ڵ�Դ����PCB�ĵط���

ͨ�������ݵĵ�Դ��ֱ�������������ĵ�Դ�ˣ�Ȼ��������Vcc�㣬�������ϰ�װС������0.1��F��0.01��F��·���ݡ��������������ݽӵض��������ӵز㣨��μ�ͼ6����

�������������������·���ݺ������������������磺˲̬��ѹ�����������������������Ӷ����ӵ����ӵĹ���С�

�ܽ�

���ܹ���PCB��Ƶ������кܶ࣬��������Ҫ�ṩһЩ�漰���ָ�������·����ƵĽ��顣��ѭ��Щ���齫�������ڶ̵�ʱ�������һ������EMC��Ҫ��ĵ�·����ơ�

��һƪ�����ص�Դ7��������·����

��һƪ��ģ���CD4051ʹ�õ�4��Ҫ��